# **Keeping Ahead of the Curve with Custom ASICs**

Authors: Edel Griffith ASIC Technical Marketing Manager Adesto Technologies edel.griffith@adestotech.com

Darren Hobbs Vice President, ASIC Sales & Marketing Adesto Technologies Darren.hobbs@adestotech.com

Sohrab Modi Chief Strategy Officer Adesto Technologies sohrab.modi@adestotech.com

#### INTRODUCTION

Disruption in electronics has always been considered as an output from the consumer market. However, for a change, a recent candidate for disruptive technology is very much the Internet of Things (IoT) in industrial markets. Since the German strategic initiative of Industry 4.0 was announced to the public at the Hannover Messe Industrie fair in 2011, the Industrial IoT (IIoT) has spread around the world and is disrupting industry in all territories. With the IoT, communication can seamlessly occur between cyber physical systems and humans in real-time and via the Internet of Services<sup>1</sup>, making possible the vision of smart factories, where a virtual copy of the physical world can be created, and decisions decentralized.

When the concept of IoT was first proposed, it was envisaged that all the data measured could be transmitted to the cloud, stored there and then the data retrieved whenever it was needed. With the daily numbers of over 2.5 quintillion bytes of data<sup>2</sup> being created and growing year by year, the concept of a purely cloud-based computing being the only solution is raising questions. Is moving all data to the cloud always a good idea? Indeed, is it always necessary? Can it be a bad idea? What happens if there is latency in communications? What is the cost associated with transmitting, gathering and storing of all this data? Does this mean an end to your IoT adoption? Is it really necessary to achieve your business goals?

While disruption is sometimes seen as being negative and bringing fear of the unknown, early adopters do in fact reap the benefits. These include the ability to be more proactive rather than reactive, having better control over inventory and facility management, being able to optimize logistics and having improved safety. To achieve these benefits however, cost, size, performance and other optimizations must be more flexible and responsive to end customer need. Doing the same thing the same way will no longer cut it. With the IIoT, demands are greater and more and more it standard becomes apparent that commercial off-the-shelf chips are not always the answer to developing each system as each provider has unique requirements. Awareness is growing that custom silicon is a compelling solution to reap the benefits from the disruptive forces of IIoT.

Custom chips or Application Specific Integrated Circuits (ASICs) are every device maker's dream, offering a single piece of silicon packaged in a single chip that is highly integrated, optimized and efficient, designed specifically for your product requirements. But over the years, ASICs have had bad press. They were seen by many as expensive and a luxury only of companies that were shipping millions of units a year and likely focused on the consumer markets.

<sup>&</sup>lt;sup>1</sup> https://conceptsystemsinc.com/the-internet-of-services-in-industrie-4-0/

<sup>&</sup>lt;sup>22</sup> Forbes. How Much Data Do We Create Every Day? The Mind-Blowing Stats Everyone Should Read https://bit.ly/2TTLHNZ

Custom ASICs were not considered possible for lower-volume industrial markets. In addition, the semiconductor industry has been laser-focused on supplying standard parts to the homogenous, large-volume consumer markets (the smart-phone being the pinnacle). Today, with the slow-down in the consumer segment, the semiconductor industry is now heavily energized to seek out new growth segments.

In this paper, we will show that custom silicon is no longer the expensive solution unique to high-volume products. With the increasing changes in technology, which will be addressed later in the paper, custom silicon is now economically viable for smaller volumes (50k+ units/year). And with the changes that the Industrial Internet of Things is bringing, we will show how custom ASICs are keeping suppliers ahead of the curve by enabling their edge processing applications through integration, power budgeting and cost reduction. With integration, it is possible to incorporate, into a single piece of silicon, in a single packaged chip, all the circuitry needed to sense, calibrate, control and communicate.

### **INDUSTRY CHANGES**

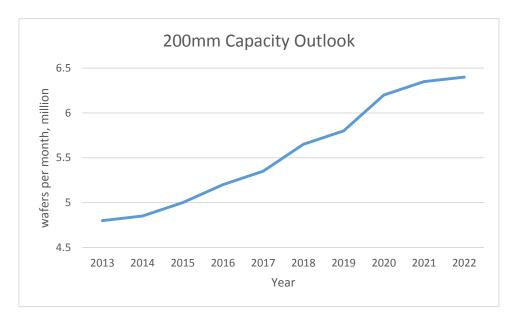

The level of changes in Industry is at an unprecedented level. Industry 4.0 is driving phenomenal growth in hardware requirements. The number of sensors being deployed is growing year on year. In the foundries the wafer capacity<sup>3</sup> is increasing and silicon revenue continues to grow year on year. Data released by SEMI shows this growth in 200mm wafer size capacity in the foundries. 200mm are typically the wafer sizes for technology nodes greater than 0.18µm.

<sup>&</sup>lt;sup>3</sup> https://m.eet.com/media/1309524/200mmforecastSEMI-min.png

Figure 1: SEMI

#### Market

Market reports from Frost & Sullivan<sup>4</sup> are predicting that the revenue from the global sensor market in IIoT alone will grow to \$11.23 billion by 2021 with a CAGR of 16.8%. While the analyst firm IDC<sup>5</sup> is projecting the worldwide spend on IoT to surpass the \$1 trillion mark in 2020 with manufacturing being one of the industries that is expected to spend the most.

As IoT adoption increases, there is also growth in the level of automation and the number of sensors being monitored. Changes in the Industrial market are occurring as the move from being reactive to being predictive occurs. This has a knock-on effect on increasing the levels of monitoring taking place and this drives an increase in the number of components in a system performing the processing and demands. communication Accurate monitoring of these sensors is vital and there also needs to be a seamless flow of correct information in and out of systems, which is driving an increase in the proliferation of specialized types of integrated chips and circuits, such as custom ASICs to meet these needs.

#### Chip Technology

In 1965, Gordon Moore highlighted how the number of transistors per square inch of integrated circuit had doubled every year since their invention. This observation became known as Moore's Law and it has

<sup>5</sup> IDC, Worldwide Semi-Annual Internet of Things Spending Guide

<sup>&</sup>lt;sup>4</sup> Frost & Sullivan, Analysis of Sensors in the Global Internet of Industrial Things Market, 2015

www.businesswire.com/news/home/20171207005963/en/IDC-Forecasts-Worldwide-Spending-Internet-Things-Reach

largely held true over the years with it being pushed to every two years from about 1975<sup>6</sup>. Technology nodes or process nodes are a reference to a semiconductor manufacturing process and the design rules that define the process. Each process node will often enable different circuit architectures. The smaller the technology or process node, the smaller the transistors available and therefore the more integration is possible<sup>7</sup>. The major drivers in pushing the decrease in size of the process nodes available in the foundries has been attributed to the consumer market space. As the demand for more features with smaller, less power-hungry and faster circuitry continues to grow, the requirement for more transistors on chip continues to increase. To meet these requirements, the transistors need to reduce in size thereby forcing the process nodes to reduce in size.

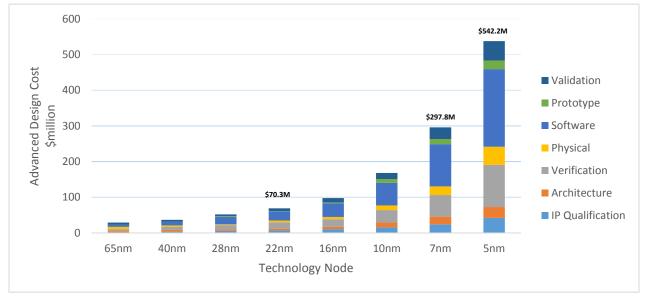

According to data published by International Business Strategies and reported by ExtremeTech<sup>8</sup>, the cost of advanced design goes from \$28.5M at 65 nanometer (nm) up to \$542.2M at 5nm.

Figure 2: IBS data on the cost of Advanced Design

<sup>&</sup>lt;sup>6</sup> Progress in Digital Integrated Electronics, IEEE Technical Digest 1975

<sup>&</sup>lt;sup>7</sup> https://en.wikichip.org/wiki/technology\_node

<sup>&</sup>lt;sup>8</sup> J.Hruska, As Chip Design Costs Skyrocket, 3nm Process Node Is in Jeopardy https://www.extremetech.com/computing/272096-3nm-process-node

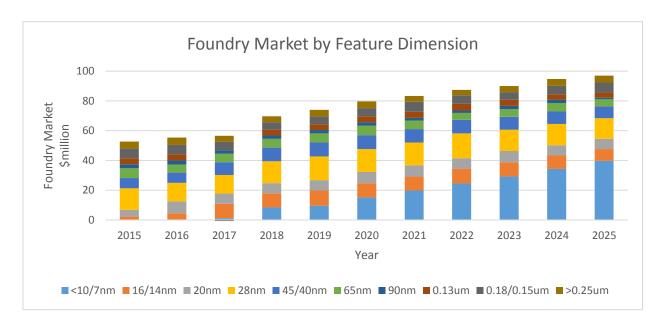

Reports by SEMI<sup>9</sup> show that the foundry market is projected to grow to \$97.5 billion by 2025. The high-volume markets will continue to push for technological improvements and be part of the bleeding edge nodes, thus freeing up the demand on more mature nodes. When we think about the bleeding edge technologies of <20nm, we think of digital circuits and how optimization at these nodes tends to be centered around the digital functionality. That is not to say that there are not analog circuits at these nodes. However, it should be noted, that analog circuits do not always directly benefit from the effects of scaling like digital circuits do. And in actual fact, reducing the size of analog components does not improve always performance, and having them in close proximity to noisy digital circuits can interference cause in the analog performance<sup>10</sup>. Estimates of process node usage by SEMI show that over 50% of the demand will still be for processes greater than 20nm and also that production is on the rise at older but cost-effective technology nodes<sup>11</sup>. So, what does this mean? The drive

for more content for automotive, industrial, IoT and mobile applications are driving this need for 200mm wafer demand and production in older technologies. It is great news for developers of products for the Industrial IoT. Advanced analog and digital circuitry to sense and measure from the large number of sensors can readily be developed on these mature nodes. These mature nodes have been well tested in the past and therefore are fully de-risked. With the foundries wanting to maximize fabrication (fab) utilization across all process nodes, now more than ever these fully depreciated fabs are offering costs that are much lower than the bleeding edge processes. Fab utilization is the total percentage of the plant and equipment that is in production use in any given time frame. Foundries want to maximize this number, as the machines are running regardless of the volume throughput and therefore they want to get the most usage out of them. The higher the utilization rate, the more volume that has been processed and therefore the more stable and reliable the processing becomes.

<sup>&</sup>lt;sup>9</sup> Dr. Handel Jones, Semiconductor Industry from 2015 to 2025, International Business Strategies (IBS) www.semi.org/en/node/57416

<sup>&</sup>lt;sup>10</sup> https://semiengineering.com/mixed-signal-issues-worse-at-10-7nm

<sup>&</sup>lt;sup>11</sup> https://www.eetimes.com/author.asp?section\_id=36&doc\_id=1334312

Figure 3: Foundry Market by Feature Dimension

As a result, there are excellent opportunities to leverage these technology nodes for the generation of custom ASICs for the IIoT and to do so at much lower costs than would have been thought previously.

# EDGE COMPUTING

Earlier we discussed whether there is always a need to send all data to the cloud to achieve the desired business goals. In order to perform the level of monitoring needed, we need to install all the required sensors – and as already discussed, the numbers of sensors being deployed is growing at a large rate. In some cases, these sensors are placed in difficult to reach locations and running off battery power. Additionally, some remote locations mean communication constraints, so it is not always possible to communicate with the cloud when needed. So, while the ideal is to sense, measure and process all the data immediately and make intelligent decisions, the reality is that it is not always possible.

In real-time control, system processing can be performed at the source. This means that the data can be analyzed straight away, and decisions made quickly. A decision can then be made as to what data needs to be stored and what data must be sent to the cloud versus the data that is no longer required. This concept has become known as edge processing or edge computing. Edge processing involves bringing the processing power closer to the sensor edge where the physical world and the origins of digital data meet. Edge processing means response time is shortened and only the data that is truly required is transmitted. This helps to unburden the network and cut communication costs.

Edge processing is not without its difficulties, however. By bringing the processing tasks right to the sensor edge, there can quite often be space constraints. Also, as we mentioned previously, the sensors can run off battery power and therefore power budgets available for processing circuitry can be demanding. Implementing a solution with discrete components while meeting demanding power budgets can be difficult.

# CUSTOM SOLUTIONS ENABLING THE EDGE

The arrival of the Industrial Internet of Things has placed many demands on technology. We need to be able to monitor the data from large numbers of sensors which can be in space-constrained locations, working on battery power and with communications latency issues. Ideally, the sensors used would produce an electric signal that is directly proportional to the physical quantity that is being measured and therefore would allow a linear transfer function. However, this is not the case and the ideal sensor does not exist<sup>12</sup>. Therefore, we need to be able to monitor the sensor with better-than-ever accuracy, allow for these inherent non-idealities of sensors, react to the information received, and perform key functions based off that information. And then we need to be able to guickly store the data required in the cloud to be accessed whenever it is needed.

#### Integration

Custom silicon was historically considered the luxury of high-volume shipments. However, since advanced semiconductor nodes track consumer high-volume segments, the more mature process nodes have opened up for lower-volume products. This means that custom ASICs are now possible for many companies who would previously have found such designs out of their budgets.

Even what seems like a moderately simple printed circuit board can contain hundreds of components. Add to this the overhead associated with specifying, purchasing and testing, the time and cost can be considerable in choosing to go the discrete component path. And this is all before you consider risks of obsolescence and security of your intellectual property.

With a custom ASIC, you can integrate all your analog and digital circuitry onto one single piece of silicon. Added to that you can include a microprocessor or microcontroller, memory (Flash and SRAM), various interfaces and wired or wireless communication protocols.

Integration can give major surface area size savings – for example, a custom off-the-shelf 12-bit Digital-to-Analog Converter (DAC) discrete component may have a physical area of 10mm<sup>2</sup>. The same DAC with equivalent performance integrated into a custom chip occupies just 0.1mm<sup>2</sup>. Later in this article we will share case studies that show how customers have achieved 80-90% area savings on their systems by using custom silicon versus discrete component solutions.

<sup>12</sup> https://bit.ly/2RMudWh

Figure 4: Visual representation of benefits of custom integration

#### **Bill of Material Cost Reduction**

Custom silicon not only leads to large savings in area, but also significant savings on your bill of material (BOM) costs. In particular, for the Industrial Internet of Things where the lifetime of products can be 10 years or more, the return on investment using custom silicon can be considerable. Also, with integration, you are moving from having all the costs associated with sourcing, storing and physical placement of large numbers of components, down to one custom chip which has incorporated all this functionality.

#### **Protecting Intellectual Property**

It is relatively trivial for a competitor to reverse-engineer a circuit board consisting of off-the-shelf semiconductor components. However, it is exceptionally difficult, if not inconclusive to reverse engineer an integrated circuit. Integration can protect the hard-earned intellectual property from been copied.

# CASE STUDIES

#### Industrial

An industrial company in the oil and gas market developed their existing solution using commercial off-the-shelf discrete components. They were shipping in the region of 60k units per year. The cost of the solution was extreme and did not offer the flexibility the company needed if they were to be able to offer their end customer the advantages they desired \_ namelv maximizing production while minimizing operating costs and being compatible with linear and rotary valves and actuators. High reliability was also a key requirement due to potential hostile working environment of the product. The company determined that they could benefit from a custom solution with:

- The ability to allow for portfolio tiering and expansion

- Multiple sensor interfaces (pressure, temperature, diagnostics)

- Integrated smart control loop

- Accurate value positioning

- Multiple communications protocols

- Integrated Arm processor and PIC controller

- Intrinsically safe by design

- Power efficient

As well as meeting the needs of their end customer, of being able to maximize production while minimizing operating costs and being compatible with different valves and actuators, this major supplier of equipment for the oil and gas market wanted to incorporate product tiering into the ASIC, something that was not economically possible previously when using discrete components. Central to the design discussions were the sensing and measurement needs, the control, programmability, and connectivity needs and finally the security needs for the final solution. A solution using TSMCs 0.18um CMOS process was delivered featuring:

- Analog front end (AFE) comprising 14-bit SAR Analog-to-Digital Converter (ADC), 12-bit control DAC, power switches, analog multiplexers and operational amplifiers

- Multiple industrial communications interfaces including FOUNDATION Fieldbus and Highway Addressable Remote Transducer (HART)

- Arm Cortex-M4 CPU core

- PIC microcontroller

- Flash and SRAM memories

- Multiple peripheral interfaces including SPI, UART, I<sup>2</sup>C and Parallel

The resulting solution which contained all the above functionality achieved the following results for the end customer:

| Results                                                                                     |

|---------------------------------------------------------------------------------------------|

| Bill of materials cost reduction of 85%                                                     |

| Substantial reduction in the physical footprint with a custom ASIC in a 19mm x 19mm package |

| Power efficiency, meeting the low-power<br>budget supplied from the 4-20mA control<br>loop  |

| Design for portfolio tiering                                                                |

| Investment breakeven 42k units                                                              |

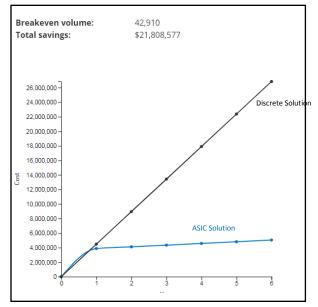

Examination of the results also show that this customer broke even on the ASIC investment after shipping over 42k units and will have estimated cost savings of over \$21m over the accumulated cost of the lifetime of the project.

Figure 5: Comparison of ASIC solution vs Discrete Solution total savings including breakeven volume

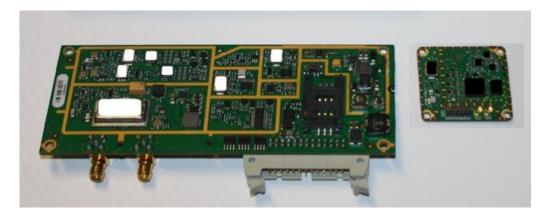

In another case study, a company was developing Machine-to-Machine (M2M) technology in the area of mobile satellite services. They were at a run rate of 100k units per year. This is a very niche area of wireless communications, providing twoway voice and data communications for mobile assets in remote locations. Reducing the system size and being able to guarantee signal quality and enhanced connectivity while keeping costs low are key concerns. While the company had already moved from a fully discrete solution by using an Application Specific Standard Product (ASSP) on their board, the product was still too generic for their requirements, and was therefore not optimized for the performance

they required. It was inefficient and costly. As a result, they were in a "make do" situation and being challenged by their end customer on performance and price.

By going the custom ASIC route, the company was able to specify exactly the requirements they wanted, with key criteria including:

- Smaller physical footprint

- Improved performance

- Lower power consumption

- Decreased cost

The custom ASIC was developed in 12 months on a 0.18um RF CMOS process from TSMC and included:

Integrated transmitter and receiver blocks (L-band receiver to support multiple modulation schemes)

- On-chip calibration functionality (RC Time constant, IP2, Image Rejection and IQ Gain/Phase)

- Embedded algorithms for DC offset correction

The resulting solution which contained all the above functionality achieved the following results for the end customer:

#### Results

55% reduction in the physical size of the product

Improved signal integrity and reliability

57% reduction in power consumption

80% reduction in the bill of material costs

Investment breakeven 175k units

Figure 6: Before and after of product size comparison (resultant board is on the right)

## CONCLUSION

While the Industrial Internet of Things offers many opportunities to enhance the efficiency and control of our processes and systems, and increase our business potential, there are many challenges. In this new era, where the cyber world is meeting the physical world, developing edge computing systems using the same tried and tested methods of the past with commercial off-the-shelf electronic components is no longer a viable approach. Considering the heterogeneous requirements at the industrial edge, no one size fits all. Recent advancements in technology mean we can now leverage custom ASICs to provide optimized performance, lowest power, and smallest area at viable economies for the IIOT.

Return to <u>IIC Journal of Innovation landing page</u> for more articles and past editions.

The views expressed in the *IIC Journal of Innovation* are the contributing authors' views and do not necessarily represent the views of their respective employers nor those of the Industrial Internet Consortium, now incorporating OpenFog.

© 2019 The Industrial Internet Consortium and OpenFog logos are registered trademarks of Object Management Group<sup>®</sup>. Other logos, products and company names referenced in this publication are property of their respective companies.